HDI PCB設計中的阻抗匹配

HDI PCB設計中的阻抗匹配

阻抗匹配是配置負載輸入阻抗或其信號源輸出阻抗的方式。執行它以實現最大功率傳輸并減少來自負載的信號反射。換句話說,為了適當的阻抗控制,負載阻抗必須等于傳輸線的特征阻抗。當傳輸的信號沒有反射時,表明負載已經吸收了所有的信號。HDI 中的阻抗匹配完全是為了避免傳輸故障,尤其是由于電阻和 PCB電介質造成的損耗。

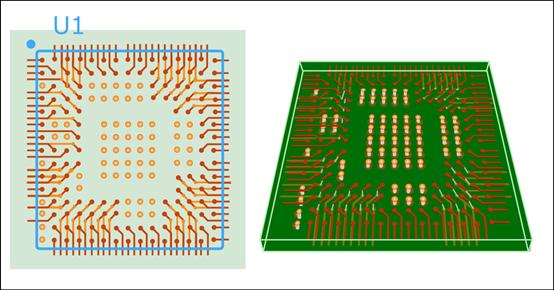

微孔可用于為阻抗匹配系統創建便于生產的 PCB走線。BGA逃逸布線技術和狗骨扇出結構可用于在 HDI 中實現阻抗匹配。

PCB走線何時需要阻抗匹配?

阻抗匹配由信號的陡度和上升/下降時間決定,而不是由頻率決定。如果信號的上升/下降時間(以 10% 至 90% 為基準)短于跡線延遲的6 倍,則稱為高速信號。在這里,應該進行精確的阻抗匹配。

HDI阻抗匹配的挑戰

在 HDI 中實現阻抗匹配時,設計人員會遇到以下挑戰:

在高密度互連HDI PCB設計中,組件具有較小的焊盤到焊盤間距,例如 BGA。間距小于或等于 0.65 毫米的 BGA 使布線和控制其寬度具有挑戰性。在這種情況下,可以使用焊盤內過孔和 BGA 逃逸布線技術。

帶有盲孔的焊盤中的過孔是一個優勢,因為它們避免了過孔殘端,從而提高了信號完整性。

在需要阻抗控制布線的 HDI 板中,精心設計的走線和堆疊對于確保阻抗與信號標準一致至關重要。

為 HDI 阻抗調整設計走線寬度

走線的阻抗由其距參考平面的寬度和高度決定。在使用細間距 BGA 的 HDI 板中,仔細選擇走線寬度和高度以避開焊盤和焊盤中通孔之間的走線。

使用 HDI PCB設計中的 BGA 逃逸布線進行阻抗控制

在處理高密度互連時使用了幾個 BGA 組件。為了使走線進出高引腳數球柵陣列的底部,需要一種逃逸布線方案。在某些情況下,需要受控阻抗(例如 FPGA 和其他高速組件),BGA 逃逸布線可能具有挑戰性。

設計電路板時要使用的逃逸布線策略很大程度上取決于 BGA 間距,它定義了允許放置在焊球之間的走線寬度。走線的細度還取決于制造商的限制、層堆疊和必要的阻抗。選擇逃逸路由方案時,請記住以下準則。

用于中等層數的細間距 BGA 的逃逸布線技術從頸縮方法開始,因為跡線被布線進出 BGA。

外部走線可以直接布線到電路板上的第一排焊盤上。

球柵陣列上第二行焊盤的跡線寬度顯著減小,以便它可以安裝在第一行焊盤之間。

要到達其余行的內墊,請穿過內層。通常,每個信號層路由到兩行,同時限制阻抗和HDI 串擾。

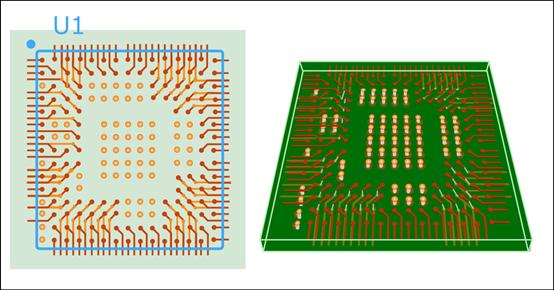

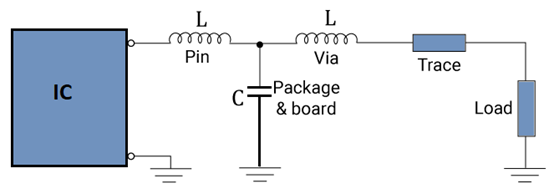

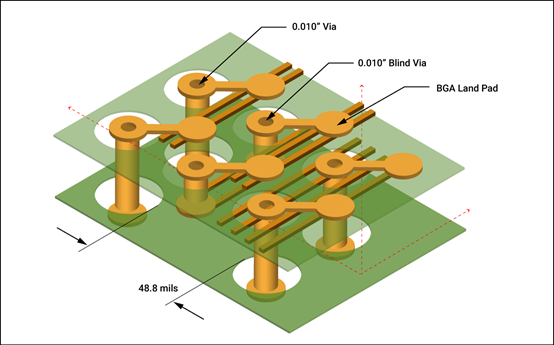

Dogbone fanout 是最流行的 BGA 逃逸布線和扇出方法(如下圖所示)。這種扇出技術有助于在更靠近焊盤的焊盤中放置通孔。由于元件不是通過通孔直接焊接到焊盤上,因此不需要進行填充鍍覆。1 mm BGA 和 0.8 mm BGA 可能適用于狗骨扇出。

當 BGA 間距小于 0.5 mm 時,最好采用 microvia-in-pad 逃逸布線技術。微通孔直接放置在焊盤中,而不是將小跡線布線到焊盤的側面。為了防止焊料芯吸到電路板的背面,微孔填充有導電環氧樹脂并鍍有銅。

用于 BGA 逃逸布線的微孔

如果焊盤尺寸(包括圓環)對于細間距 BGA 來說足夠小,則使用微孔進行內層 BGA 逃逸布線。以下特征將微孔與傳統孔區分開來:

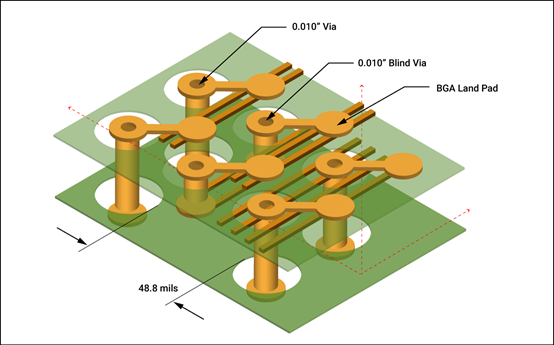

過孔長度:過孔最多只能穿過一層或兩層。如果標準厚度 PCB具有非常高的層數,則通孔可以跨越更多層,但這需要額外的制造程序。盡可能使用跨越單層的堆疊盲孔和埋孔。

微孔縱橫比:微孔縱橫比(深度除以直徑)應為0.75:1。讓我們通過考慮 32 層厚板的示例來理解相同的內容。由于層厚(對于 2 層磁芯)為 2 密耳,因此直徑不應小于 2.7 密耳。

微通孔只能安全地機械鉆孔到 8 密耳,但是由于頻繁的鉆孔斷裂,8 密耳的機械 PCB鉆孔費用可以接近激光鉆孔的價格。機械通孔的吞吐量低于激光鉆孔的通孔,因為必須小心地進行機械鉆孔以避免鉆頭斷裂。因此,一旦您開始使用激光鉆孔,您就會看到每塊板的總成本下降。

要在 0.8 毫米間距 BGA 上使用狗骨扇出,走線寬度必須為 10 密耳或更小,微孔必須更小(約 6 密耳)。對于更細間距的球柵陣列(0.5 毫米),使用填充和電鍍的焊盤內微孔通過 7 mil 或 8 mil 走線布線到內層中。這將在相鄰焊盤之間提供足夠的間距。

無論設計風格如何,微孔都可以堆疊或交錯排列,以達到所需的布線密度。通過IPC 6012要求,以確保微孔和周圍環形圈的尺寸具有最佳可靠性。焊盤內微孔在 BGA 逃逸布線中的相關性可以通過以下事實來理解:BGA 間距在某些情況下可以低至 0.3 毫米。

如何放置盲孔以進行逃逸布線

內層布線空間的盲孔方法。

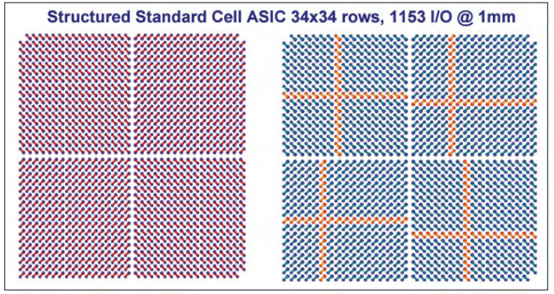

盲孔是一種寶貴的 HDI 設計方法,可以釋放額外的內層布線空間。當在通孔之間使用時,這些類型的過孔使內層的布線空間加倍。它允許額外的走線連接內部 BGA 行上的引腳。見上圖;在這里,在這個 1.0 毫米 BGA 表面上的通孔之間只有兩條走線可以逃逸。但是,現在盲孔下方可以有 6 條走線,這將布線空間增加了 30%。

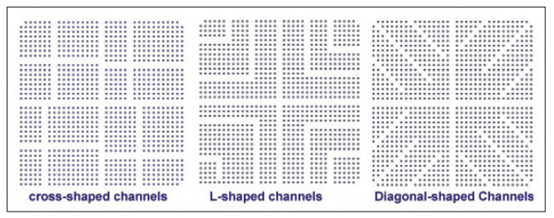

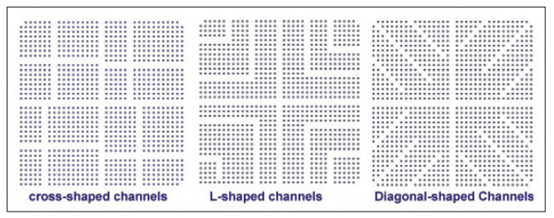

使用這種方法,需要四分之一的信號層來連接高 I/O BGA。盲孔以十字、L 形或對角線圖案放置,以形成林蔭大道。電源和接地引腳分配決定了使用哪種配置。

以交叉、L 形或對角線形狀放置盲孔會在內層上創建林蔭大道,以允許更高密度的布線和逃逸。

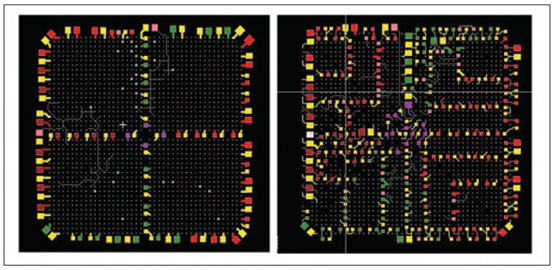

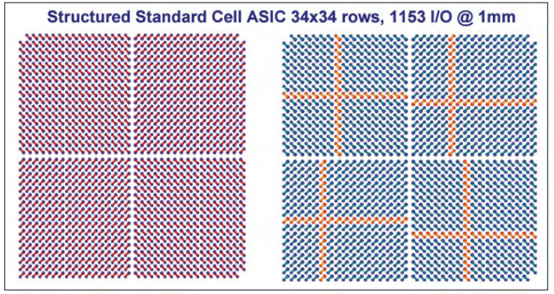

插圖顯示了放置盲孔以在 BGA 內創建林蔭大道以改善突破。左:BGA 的傳統 4 象限扇出;右圖:添加了十字形盲孔,允許在內層上創建的林蔭大道中增加 48 個逃逸通道,從而減少了突破器件所需的 4 個。

Happy Holden 解釋說:“每層可以連接更多的走線,還可以通過使用林蔭大道創建額外的布線空間來減少信號層的總數。盲孔用于創建四個十字形林蔭大道(如圖所示)。新設計的林蔭大道每層提供 48 個更多的逃逸通道(8 x 6 走線),并提高了內部走線的信號完整性。它允許移除兩個布線層和兩個參考平面。”

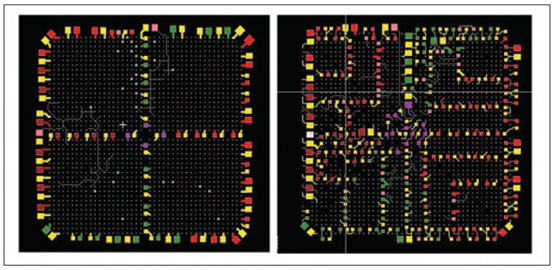

此外,他說:“在電路板的次級側,可以觀察到使用盲孔創建林蔭大道的另一個優勢。通孔橫跨整個電路板,但林蔭大道現在在 BGA 內開放(如圖所示)。左圖顯示了由 BGA 下的 104 個過孔連接的 58 個分立器件。在右側,林蔭大道可以通過共享 366 個過孔連接 183 個分立元件。”

這些圖顯示了兩個 BGA 的背面。一種是帶有通孔的傳統象限扇出,允許 58 個分立器件。另一個利用林蔭大道的盲道,其中可以連接 183 個分立元件。

扇出部分長度和走線寬度

在使用高速 IC 時,阻抗幾乎總是一個因素。在檢查扇出部分的長度時,扇出布線和阻抗控制之間的關系開始發揮作用。由于過孔的走線長度(如果存在)和寄生電容/電感,BGA 扇出部分將具有其阻抗。

首先,檢查信號帶寬以確定信號是否會在走線阻抗上拾取。如果走線長度明顯小于對應于帶寬高端的波長,則可以忽略 BGA 扇出的走線部分。最好的方法是計算負載阻抗,它是扇出走線長度的函數,以及由扇出走線創建的網絡輸入阻抗(頸縮后)。

對信號波長所需的長度使用 10% 的限制作為一個很好的近似值。對拐點頻率為 20GHz 的數字信號謹慎的 10% 限制將導致臨界長度為 0.73mm(FR4 基板中的帶狀線)。這意味著更大的 IC,比如 FPGA,需要為單端和差分對提供阻抗匹配的扇出。

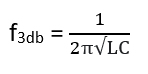

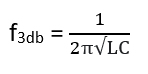

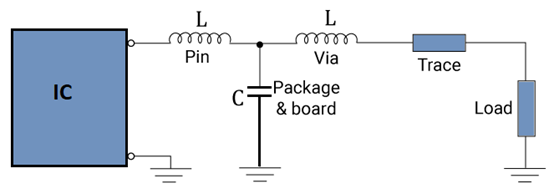

過孔電感、電路板和焊盤之間的寄生電容以及 IC 中的引腳電感至關重要。低通T濾波器電路由這些部分組合而成。3dB 截止頻率只是可以從 LC 諧振電路評估的典型數字,前提是通孔電感設置為等于引腳電感。該 T 濾波器電路用作阻抗匹配電路,修改驅動器 IC 的輸出阻抗。

以通孔電感、電路板與焊盤之間的寄生電容以及引腳電感為主要部件的低通T濾波器電路。

如果不確定將扇出跡線連接到內部跡線的過孔部分阻抗,則扇出部分的阻抗匹配是困難的。然而,只要過孔部分很短并且直接跨越幾層,這個事實就可以被忽略。包括通孔和內部走線在內的總輸入阻抗由跨越少量層的內部走線阻抗決定。這就是為什么通常不考慮通孔阻抗的原因。

主要缺點是高速 BGA 組件(例如 FPGA)可能需要回鉆以去除 BGA 扇出下方的殘留通孔存根。使用 HDI 時,使用直徑非常小的盲孔、埋孔和激光鉆孔微孔(根據 IPC 小于 6 密耳),這消除了背鉆孔并將通孔電感限制在跨越層的厚度。

由于層厚和到走線參考平面的距離會隨著層數的增加而減少,因此必須減小走線寬度以補償并將阻抗保持在適當的值。如果您使用差分對,請考慮走線耦合。為了實現阻抗控制,帶有集成場解算器的PCB設計軟件可以幫助為 HDI 層堆疊設計正確的走線寬度。

為什么HDI PCB設計中走線寬度不能大于焊盤尺寸?

走線的寬度與其阻抗成正比,并且在您進入 HDI 狀態時起著至關重要的作用。過孔將變得非常小,以至于一旦走線寬度足夠小,就必須將它們制造為微孔。

如果阻抗控制的走線寬度過寬,要么減小PCB層壓板的厚度以縮小它,要么增加焊盤尺寸。從可靠性的角度來看,只要焊盤尺寸超過 IPC 標準中規定的數字就可以了。

為 PCB堆疊創建阻抗曲線,并將該寬度用作設計指南。在計算阻抗控制所需的寬度后,只需將此值指定為設計規則即可。最好針對建議的走線寬度執行串擾模擬,以查看是否會導致過度串擾。

HDI 中的阻抗匹配與保持信號質量有關,因為組件和走線都間隔很近。因此,控制阻抗成為一項令人難以置信的任務。有效使用微孔是阻抗匹配 HDI 系統的關鍵。更細間距 BGA 的逃逸布線技術和狗骨扇出方法可用于實現 HDI 中的阻抗匹配。

豐樂壹博專業PCB設計、PCB Layout、PCBA一站式生產。

阻抗匹配是配置負載輸入阻抗或其信號源輸出阻抗的方式。執行它以實現最大功率傳輸并減少來自負載的信號反射。換句話說,為了適當的阻抗控制,負載阻抗必須等于傳輸線的特征阻抗。當傳輸的信號沒有反射時,表明負載已經吸收了所有的信號。HDI 中的阻抗匹配完全是為了避免傳輸故障,尤其是由于電阻和 PCB電介質造成的損耗。

微孔可用于為阻抗匹配系統創建便于生產的 PCB走線。BGA逃逸布線技術和狗骨扇出結構可用于在 HDI 中實現阻抗匹配。

PCB走線何時需要阻抗匹配?

阻抗匹配由信號的陡度和上升/下降時間決定,而不是由頻率決定。如果信號的上升/下降時間(以 10% 至 90% 為基準)短于跡線延遲的6 倍,則稱為高速信號。在這里,應該進行精確的阻抗匹配。

HDI阻抗匹配的挑戰

在 HDI 中實現阻抗匹配時,設計人員會遇到以下挑戰:

在高密度互連HDI PCB設計中,組件具有較小的焊盤到焊盤間距,例如 BGA。間距小于或等于 0.65 毫米的 BGA 使布線和控制其寬度具有挑戰性。在這種情況下,可以使用焊盤內過孔和 BGA 逃逸布線技術。

帶有盲孔的焊盤中的過孔是一個優勢,因為它們避免了過孔殘端,從而提高了信號完整性。

在需要阻抗控制布線的 HDI 板中,精心設計的走線和堆疊對于確保阻抗與信號標準一致至關重要。

為 HDI 阻抗調整設計走線寬度

走線的阻抗由其距參考平面的寬度和高度決定。在使用細間距 BGA 的 HDI 板中,仔細選擇走線寬度和高度以避開焊盤和焊盤中通孔之間的走線。

使用 HDI PCB設計中的 BGA 逃逸布線進行阻抗控制

在處理高密度互連時使用了幾個 BGA 組件。為了使走線進出高引腳數球柵陣列的底部,需要一種逃逸布線方案。在某些情況下,需要受控阻抗(例如 FPGA 和其他高速組件),BGA 逃逸布線可能具有挑戰性。

設計電路板時要使用的逃逸布線策略很大程度上取決于 BGA 間距,它定義了允許放置在焊球之間的走線寬度。走線的細度還取決于制造商的限制、層堆疊和必要的阻抗。選擇逃逸路由方案時,請記住以下準則。

用于中等層數的細間距 BGA 的逃逸布線技術從頸縮方法開始,因為跡線被布線進出 BGA。

外部走線可以直接布線到電路板上的第一排焊盤上。

球柵陣列上第二行焊盤的跡線寬度顯著減小,以便它可以安裝在第一行焊盤之間。

要到達其余行的內墊,請穿過內層。通常,每個信號層路由到兩行,同時限制阻抗和HDI 串擾。

Dogbone fanout 是最流行的 BGA 逃逸布線和扇出方法(如下圖所示)。這種扇出技術有助于在更靠近焊盤的焊盤中放置通孔。由于元件不是通過通孔直接焊接到焊盤上,因此不需要進行填充鍍覆。1 mm BGA 和 0.8 mm BGA 可能適用于狗骨扇出。

當 BGA 間距小于 0.5 mm 時,最好采用 microvia-in-pad 逃逸布線技術。微通孔直接放置在焊盤中,而不是將小跡線布線到焊盤的側面。為了防止焊料芯吸到電路板的背面,微孔填充有導電環氧樹脂并鍍有銅。

用于 BGA 逃逸布線的微孔

如果焊盤尺寸(包括圓環)對于細間距 BGA 來說足夠小,則使用微孔進行內層 BGA 逃逸布線。以下特征將微孔與傳統孔區分開來:

過孔長度:過孔最多只能穿過一層或兩層。如果標準厚度 PCB具有非常高的層數,則通孔可以跨越更多層,但這需要額外的制造程序。盡可能使用跨越單層的堆疊盲孔和埋孔。

微孔縱橫比:微孔縱橫比(深度除以直徑)應為0.75:1。讓我們通過考慮 32 層厚板的示例來理解相同的內容。由于層厚(對于 2 層磁芯)為 2 密耳,因此直徑不應小于 2.7 密耳。

微通孔只能安全地機械鉆孔到 8 密耳,但是由于頻繁的鉆孔斷裂,8 密耳的機械 PCB鉆孔費用可以接近激光鉆孔的價格。機械通孔的吞吐量低于激光鉆孔的通孔,因為必須小心地進行機械鉆孔以避免鉆頭斷裂。因此,一旦您開始使用激光鉆孔,您就會看到每塊板的總成本下降。

要在 0.8 毫米間距 BGA 上使用狗骨扇出,走線寬度必須為 10 密耳或更小,微孔必須更小(約 6 密耳)。對于更細間距的球柵陣列(0.5 毫米),使用填充和電鍍的焊盤內微孔通過 7 mil 或 8 mil 走線布線到內層中。這將在相鄰焊盤之間提供足夠的間距。

無論設計風格如何,微孔都可以堆疊或交錯排列,以達到所需的布線密度。通過IPC 6012要求,以確保微孔和周圍環形圈的尺寸具有最佳可靠性。焊盤內微孔在 BGA 逃逸布線中的相關性可以通過以下事實來理解:BGA 間距在某些情況下可以低至 0.3 毫米。

如何放置盲孔以進行逃逸布線

內層布線空間的盲孔方法。

盲孔是一種寶貴的 HDI 設計方法,可以釋放額外的內層布線空間。當在通孔之間使用時,這些類型的過孔使內層的布線空間加倍。它允許額外的走線連接內部 BGA 行上的引腳。見上圖;在這里,在這個 1.0 毫米 BGA 表面上的通孔之間只有兩條走線可以逃逸。但是,現在盲孔下方可以有 6 條走線,這將布線空間增加了 30%。

使用這種方法,需要四分之一的信號層來連接高 I/O BGA。盲孔以十字、L 形或對角線圖案放置,以形成林蔭大道。電源和接地引腳分配決定了使用哪種配置。

以交叉、L 形或對角線形狀放置盲孔會在內層上創建林蔭大道,以允許更高密度的布線和逃逸。

插圖顯示了放置盲孔以在 BGA 內創建林蔭大道以改善突破。左:BGA 的傳統 4 象限扇出;右圖:添加了十字形盲孔,允許在內層上創建的林蔭大道中增加 48 個逃逸通道,從而減少了突破器件所需的 4 個。

Happy Holden 解釋說:“每層可以連接更多的走線,還可以通過使用林蔭大道創建額外的布線空間來減少信號層的總數。盲孔用于創建四個十字形林蔭大道(如圖所示)。新設計的林蔭大道每層提供 48 個更多的逃逸通道(8 x 6 走線),并提高了內部走線的信號完整性。它允許移除兩個布線層和兩個參考平面。”

此外,他說:“在電路板的次級側,可以觀察到使用盲孔創建林蔭大道的另一個優勢。通孔橫跨整個電路板,但林蔭大道現在在 BGA 內開放(如圖所示)。左圖顯示了由 BGA 下的 104 個過孔連接的 58 個分立器件。在右側,林蔭大道可以通過共享 366 個過孔連接 183 個分立元件。”

這些圖顯示了兩個 BGA 的背面。一種是帶有通孔的傳統象限扇出,允許 58 個分立器件。另一個利用林蔭大道的盲道,其中可以連接 183 個分立元件。

扇出部分長度和走線寬度

在使用高速 IC 時,阻抗幾乎總是一個因素。在檢查扇出部分的長度時,扇出布線和阻抗控制之間的關系開始發揮作用。由于過孔的走線長度(如果存在)和寄生電容/電感,BGA 扇出部分將具有其阻抗。

首先,檢查信號帶寬以確定信號是否會在走線阻抗上拾取。如果走線長度明顯小于對應于帶寬高端的波長,則可以忽略 BGA 扇出的走線部分。最好的方法是計算負載阻抗,它是扇出走線長度的函數,以及由扇出走線創建的網絡輸入阻抗(頸縮后)。

對信號波長所需的長度使用 10% 的限制作為一個很好的近似值。對拐點頻率為 20GHz 的數字信號謹慎的 10% 限制將導致臨界長度為 0.73mm(FR4 基板中的帶狀線)。這意味著更大的 IC,比如 FPGA,需要為單端和差分對提供阻抗匹配的扇出。

過孔電感、電路板和焊盤之間的寄生電容以及 IC 中的引腳電感至關重要。低通T濾波器電路由這些部分組合而成。3dB 截止頻率只是可以從 LC 諧振電路評估的典型數字,前提是通孔電感設置為等于引腳電感。該 T 濾波器電路用作阻抗匹配電路,修改驅動器 IC 的輸出阻抗。

以通孔電感、電路板與焊盤之間的寄生電容以及引腳電感為主要部件的低通T濾波器電路。

如果不確定將扇出跡線連接到內部跡線的過孔部分阻抗,則扇出部分的阻抗匹配是困難的。然而,只要過孔部分很短并且直接跨越幾層,這個事實就可以被忽略。包括通孔和內部走線在內的總輸入阻抗由跨越少量層的內部走線阻抗決定。這就是為什么通常不考慮通孔阻抗的原因。

主要缺點是高速 BGA 組件(例如 FPGA)可能需要回鉆以去除 BGA 扇出下方的殘留通孔存根。使用 HDI 時,使用直徑非常小的盲孔、埋孔和激光鉆孔微孔(根據 IPC 小于 6 密耳),這消除了背鉆孔并將通孔電感限制在跨越層的厚度。

由于層厚和到走線參考平面的距離會隨著層數的增加而減少,因此必須減小走線寬度以補償并將阻抗保持在適當的值。如果您使用差分對,請考慮走線耦合。為了實現阻抗控制,帶有集成場解算器的PCB設計軟件可以幫助為 HDI 層堆疊設計正確的走線寬度。

為什么HDI PCB設計中走線寬度不能大于焊盤尺寸?

走線的寬度與其阻抗成正比,并且在您進入 HDI 狀態時起著至關重要的作用。過孔將變得非常小,以至于一旦走線寬度足夠小,就必須將它們制造為微孔。

如果阻抗控制的走線寬度過寬,要么減小PCB層壓板的厚度以縮小它,要么增加焊盤尺寸。從可靠性的角度來看,只要焊盤尺寸超過 IPC 標準中規定的數字就可以了。

為 PCB堆疊創建阻抗曲線,并將該寬度用作設計指南。在計算阻抗控制所需的寬度后,只需將此值指定為設計規則即可。最好針對建議的走線寬度執行串擾模擬,以查看是否會導致過度串擾。

HDI 中的阻抗匹配與保持信號質量有關,因為組件和走線都間隔很近。因此,控制阻抗成為一項令人難以置信的任務。有效使用微孔是阻抗匹配 HDI 系統的關鍵。更細間距 BGA 的逃逸布線技術和狗骨扇出方法可用于實現 HDI 中的阻抗匹配。

豐樂壹博專業PCB設計、PCB Layout、PCBA一站式生產。

上一新聞:在高速PCB設計中不要跨越地平面間隙

下一新聞:PCB設計放大器接線技巧